- 您现在的位置:买卖IC网 > Sheet目录3831 > AT87C52X2-3CSUL (Atmel)IC 8051 MCU 8K OTP 30MHZ 40DIP

46

TS8xCx2X2

4184I–8051–02/08

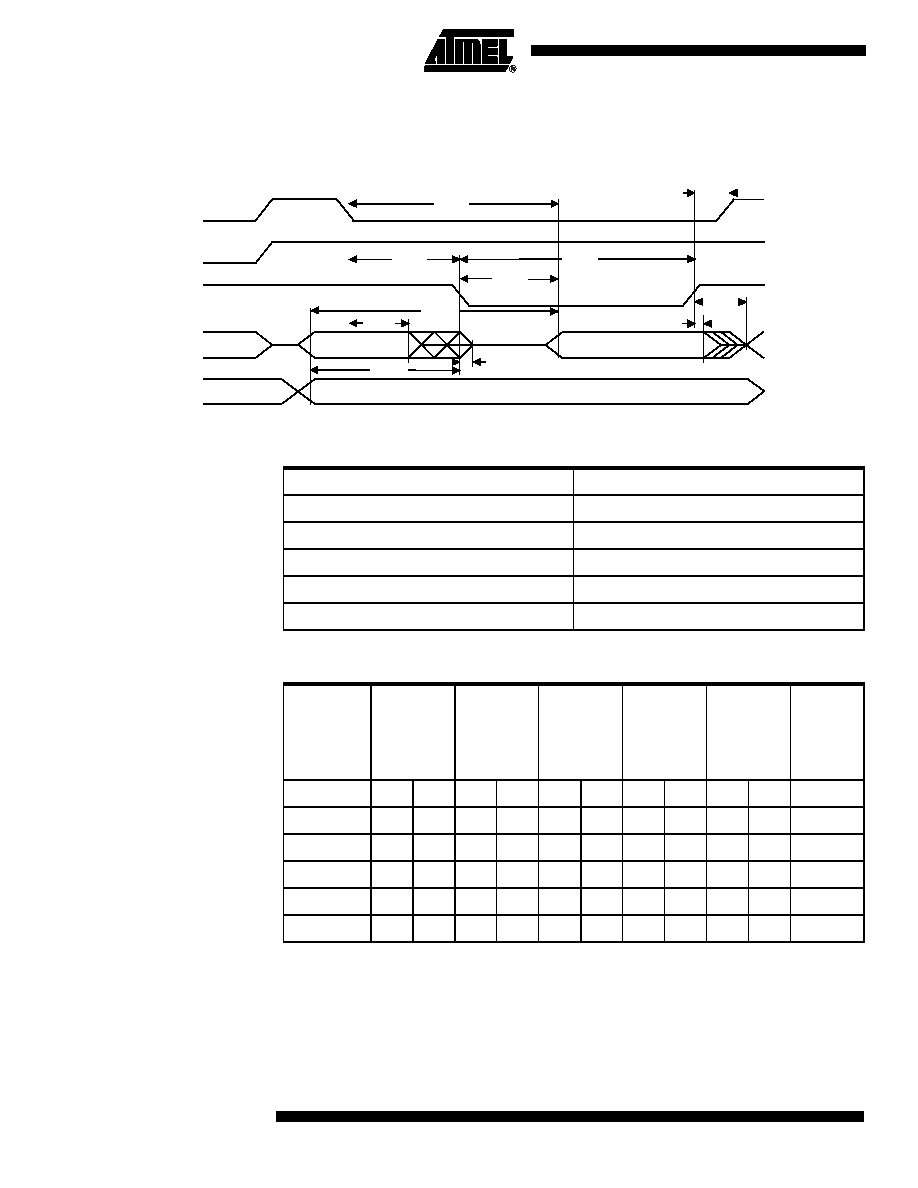

External Data Memory Read

Cycle

Figure 20. External Data Memory Read Cycle

Serial Port Timing - Shift

Register Mode

Table 32. Symbol Description

Table 33. AC Parameters for a Fix Clock

ALE

PSEN

RD

PORT 0

PORT 2

A0-A7

DATA IN

ADDRESS

OR SFR-P2

TAVWL

TLLWL

TRLAZ

ADDRESS A8-A15 OR SFR P2

TRHDZ

TWHLH

TRLRH

TLLDV

TRHDX

TAVDV

TLLAX

TRLDV

Symbol

Parameter

TXLXL

Serial port clock cycle time

TQVHX

Output data set-up to clock rising edge

TXHQX

Output data hold after clock rising edge

TXHDX

Input data hold after clock rising edge

TXHDV

Clock rising edge to input data valid

Speed

-M

40 MHz

-V

X2 mode

30 MHz

60 MHz

equiv.

-V

standard

mode 40

MHz

-L

X2 mode

20 MHz

40 MHz

equiv.

-L

standard

mode

30 MHz

Units

Symbol

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

TXLXL

300

200

300

400

ns

TQVHX

200

117

200

283

ns

TXHQX

30

13

30

47

ns

TXHDX

0

ns

TXHDV

117

34

117

200

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AT87C51RD2-SLSUM

IC 8051 MCU 64K OTP 40MHZ 44PLCC

AT87C51RD2-SLSUL

IC 8051 MCU 64K OTP 30MHZ 44PLCC

201532-4

CONN HOUSING RECEPT 104POS BLACK

AT87C54X2-SLSUL

IC 8051 MCU 16K EPROM 44PLCC

AT87C54X2-RLTUM

IC 8051 MCU 16K EPROM 44VQFP

213685-2

34P RCPT KIT,M-SERIES,CC,JS

PIC16C71-20I/P

IC MCU OTP 1KX14 A/D 18DIP

PIC18LF4510-I/P

IC MCU FLASH 16KX16 40DIP

相关代理商/技术参数

AT87C52X2-3CSUM

功能描述:8位微控制器 -MCU 256B RAM 60MHz 2.7V-5.5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-3CSUV

功能描述:8位微控制器 -MCU Microcontroller

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLRUM

功能描述:8位微控制器 -MCU 0.5um RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUL

功能描述:8位微控制器 -MCU C72X2C52 0.5m OTP RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUM

功能描述:8位微控制器 -MCU C72X2 C52 0.5 m X 2 OTP 0.5 NV RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-RLTUV

制造商:ATMEL 制造商全称:ATMEL Corporation 功能描述:8-bit Microcontroller 8 Kbytes ROM/OTP, ROMless

AT87C52X2-SLRUL

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

AT87C52X2-SLRUM

功能描述:8位微控制器 -MCU Microcontroller RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT